SCPCDLe 30/09/2022 à 11:10

je viens de faire le test et finalement ça change pas grand chose : les accès DRAM sont plus rapide, mais de pas grand chose.

programme de test :

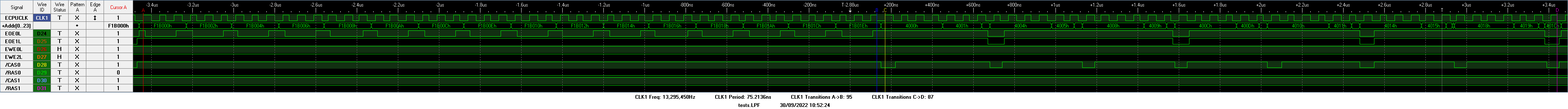

Le résultat à l'analyseur logique :

Au final :

- les accès GPU => DSP mettent 95 cycles GPU pour faire 8 accès consécutif lw

- les accès GPU => DRAM mettent 87 cycles GPU pour faire 8 accès consécutif lw

Ça prend donc qu'1 cycle de plus par accès par rapport à la DRAM.

programme de test :

.include "includes/include.inc"

.text

.68000

m68k_start::

move.w #$2700, sr

move.l #INITSTACK, sp

move.w #$FF00, INT1

move.w #$FFFF, INT2

lea gpu_code_start, a0

lea G_RAM, a1

move.l #gpu_code_end-gpu_code_start, d0

.copy:

move.l (a0)+, (a1)+

dbra d0, .copy

; start GPU

move.l #gpu_init, G_PC

move.l #1, G_CTRL

stop #$2700

.long

gpu_code_start::

.gpu

.org G_RAM

gpu_init:

movei #.readmem, r30

movei #$4000, r14

movei #D_RAM, r15

.readmem:

load (r14), r0

load (r14+1), r1

load (r14+2), r2

load (r14+3), r3

load (r14+4), r4

load (r14+5), r5

load (r14+6), r6

load (r14+7), r7

load (r15), r20

load (r15+1), r21

load (r15+2), r22

load (r15+3), r23

load (r15+4), r24

load (r15+5), r25

load (r15+6), r26

load (r15+7), r27

jump T, (r30)

nop

.68000

gpu_code_end::

dc.l 0

Le résultat à l'analyseur logique :

Au final :

- les accès GPU => DSP mettent 95 cycles GPU pour faire 8 accès consécutif lw

- les accès GPU => DRAM mettent 87 cycles GPU pour faire 8 accès consécutif lw

Ça prend donc qu'1 cycle de plus par accès par rapport à la DRAM.